Лабораторная

работа

Тема: Элементы ИМС на МДП-транзисторах и

КМОП-транзисторах

Цель: Научиться строить и анализировать работу схем

элементов ИМС средствами Electronics WorkBenck

Ход

работы:

В большинстве

цифровых устройств обработка информации производится с помощью двоичного кода.

Информационные сигналы принимают только два значения (1 и 0).

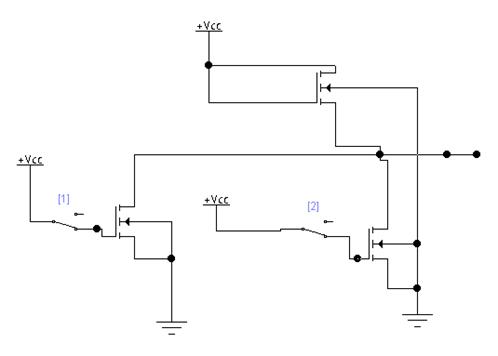

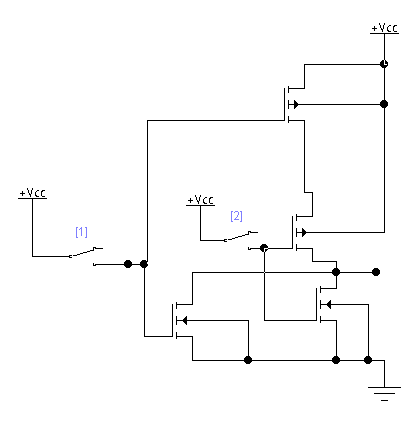

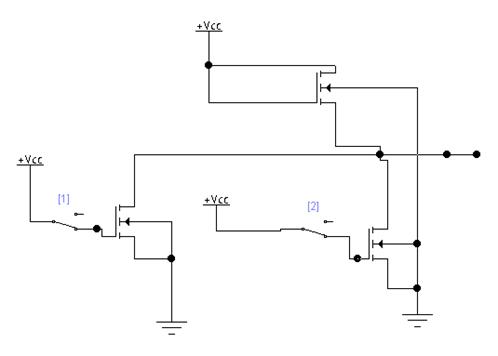

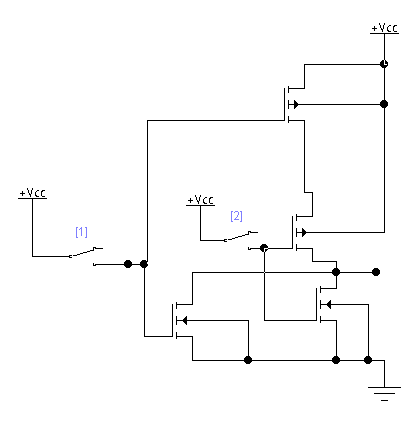

Рисунок 1- Элемент ИЛИ-НЕ на однотипном

МДП-транзисторе

В данной схеме на входы поданы два сигнала, соответствующие

логической единице. На выходе будет сигнал 0, так как два транзистора открыты и

сигнал уходит через них. При подаче высокого уровня U хотя бы на один из

выходов схемы, открывается соответствующий транзистор и на выходе

устанавливается низкий уровень сигнала. Если на обоих входах логический ноль,

то VT1 и VT2 — закрыты и на выходе формируется логическая единица.

Нагрузочный

транзистор VT3 всегда открыт.

Рисунок 2 – Изображение анализатора

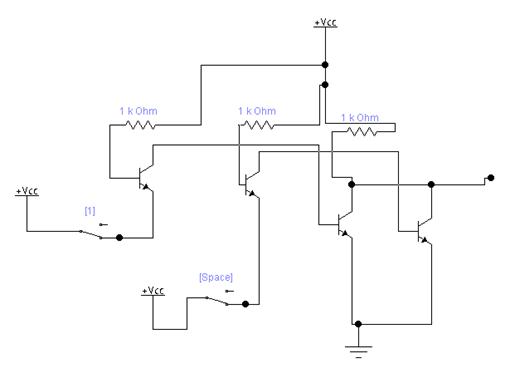

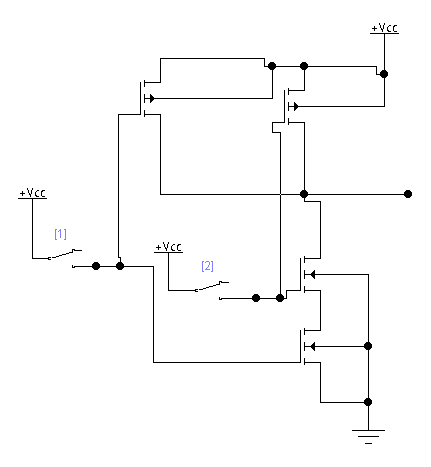

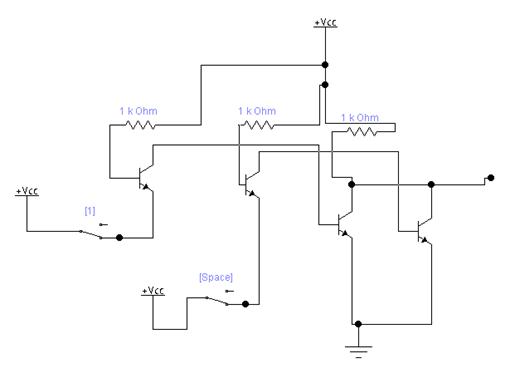

Рисунок 3- Элемент ИЛИ-НЕ на биполярном

транзисторе

Рисунок 4 –

Изображение анализатора

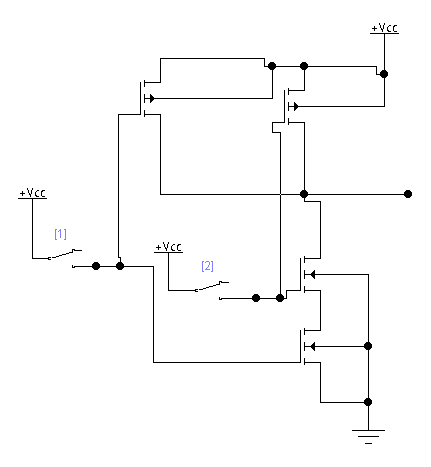

Рисунок 5 – Элемент ИЛИ-НЕ на КМОП-транзисторе.

Рисунок 6 – Результаты с анализатора

Рисунок

7 – Элемент И-НЕ на КМОП-транзисторе

Рисунок 8 –

Результат с анализатора

Низкий

уровень сигнала на выходах управляющих транзисторов VT1 и VT2 переводит их в

закрытое состояние. При этом последовательно соединённые нагрузочные

транзисторы VT3 и VT4 открыты и на выходе схемы устанавливается напряжение

высокого уровня, равное напряжению источника питания.

Если хотя бы

на один вход поступает сигнал логической единицы, то открывается

соответствующий управляющий транзистор (VT1 или VT2), а связанный с ним нагрузочный

(VT3 или VT4) закрывается. На выходе схемы устанавливается логический ноль.

Другие работы по теме:

Электронные ключи

Назначение и параметры электронных ключей. Диодные, транзисторные ключи. Временные диаграммы тока и выходного напряжения идеального ключа. Схема и характеристики режима работы ключа на биполярном транзисторе. Время переключения ключей на транзисторах.

Генератор на микросхеме

Функциональный генератор, описываемый в этой статье, построен на микросхеме КР580ГФ24, предназначенной для тактирования микропроцессора КР580ВМ80. К достоинствам генератора относится способность работать на частотах до 20 МГц, при этом хорошая форма треугольного напряжения сохраняется до частоты примерно 5 МГц.

Жидкие кристаллы 3

Жидкие кристаллы (ЖК) - это вещества, способные под электрическим напряжением изменять величину пропускаемого света. Современные ЖК - мониторы называют - LCD-монитор, плоскими панелями, активными матрицами двойного сканирования, тонкопленочными транзисторами, они изящны на вид, компактны, экономичны, обеспечивают высококачественное контрастное, яркое, отчетливое изображение, но цена более высокой, чем у мониторов с ЭЛТ.

Расчет схемной модели кремниевого дрейфового транзистора

Рассчет параметров П-образной эквивалентной схемы транзистора включенного по схеме с ОЭ для НЧ и ВЧ. Зависимость максимальной частоты от напряжения коллектор-эмиттер. Описание технология изготовления дрейфового транзистора, структура n-p-n-перехода.

Схема трансформаторного усилителя

Построение принципиальной схемы однотактного резистивного трансформаторного усилителя и расчет его параметров. Определение коэффициентов усиления по току, напряжению и сопротивлению для включения. Изучение особенностей микросхемы на транзисторах.

Интегральная и микропроцессорная схемотехника

Рабочая программа курса «Интегральная и микропроцессорная схемотехника» Введение . Роль интегральной электроники в развитии современной науки и техники. Этапы перехода от дискретных элементов к интегральным микросхемам. Успехи, достигнутые в области разработки полупроводниковых приборов и микросхемотехники.

Интегра льная микро схе ма

Интегра́льная (микро)схе́ма (ИС, ИМС, м/сх, англ. integrated circuit, IC, microcircuit), чип, микрочи́п (англ. microchip, silicon chip, chip — тонкая пластинка — первоначально термин относился к пластинке кристалла микросхемы) — микроэлектронное устройство — электронная схема произвольной сложности, изготовленная на полупроводниковом кристалле (или плёнке) и помещённая в неразборный корпус, или без такового, в случае вхождения в состав микросборки.

Описание схемы автомата световых эффектов Бегущие огни

1 ОПИСАНИЕ СХЕМЫ АВТОМАТА СВЕТОВЫХЭФФЕКТОВ «БЕГУЩИЕ ОГНИ» Трехфазный мультивибратор собран на транзисторах VT1-VT3, в их коллекторные цепи включены светодиоды HL1-HL12, разделенные на три группы по четыре последовательно. Транзисторы поочередно открываются и включают соответствующие светодиоды.

Коммутаторы аналоговых сигналов. Устройство и принцип действия

Устройство коммутаторов аналоговых сигналов. Сущность коммутации сигналов - метода, с помощью которого сигналы, поступающие от нескольких источников, объединяются в определенном порядке в одной линии. Многоканальные, матричные коммутаторы, мультиплексоры.

Электронный ключ на полевом транзисторе

Электронные ключи – элементы, производящие под воздействием управляющего сигнала различные коммутации в импульсных и цифровых устройствах. Схемы электронных ключей на полевых транзисторах. Принцип их работы, схожесть с ключами на биополярных транзисторах.

Расчет оконечного каскада передатчика

Параметры расчета предварительного и оконечного каскадов передатчика на биполярных транзисторах. Расчёт оконечного каскада. Параметры транзистора 2Т903А. Результат расчёта входной цепи. Результаты расчёта коллекторной цепи. Расчёт предоконечного каскада.

Расчет схемы мультивибратора на полевых транзисторах

Электронная вычислительная техника. Описание схемы устройства, расчет фантастронного генератора пилообразного напряжения. Генераторы прямоугольных импульсов, линейно-изменяющегося напряжения, ступенчато-изменяющегося напряжения, синусоидальных колебаний.

Разработка передатчика для радиовещания в синхронной сети

Использование синхронных сетей радиовещания для повышения эффективности работы передатчиков и улучшения слышимости РВ передач на низких и средних частотах. Разработка структурной схемы передатчика. Выбор усилительного элемента в выходном каскаде.

Дослiдження цифрових iнтегральних мiкросхем

Принципи роботи основних логiчних функцiй цифрової технiки на прикладi базових елементiв серii К155. До найпростіших логічних елементів відносяться такі, як "АБО", "I-НЕ", "НЕ" а також їх комбінації. Основні принципі роботи цих елементів, їх схеми.

Биотелеметрические сигналы и их калибровка

Калибровка биотелеметрических сигналов электрокардиограмм, псевмограмм для получения количественных сведений об уровне сигналов. Симметричные и несимметричные мультивибраторы на биполярных транзисторах, расчет при заданном напряжении источника питания.

Расчет усилителя низкой частоты

Определение параметров работы двухкаскадного усилителя тока с непосредственной связью, выполненного на германиевых (Ge) транзисторах структуры n-p-n по заданным показателям. Основные расчеты показателей преобразования напряжения, коэффициентов усиления.

Импульсно-статические, динамические, квазистатические триггеры

Признаки импульсно-статических триггеров. Динамические триггеры, выполненные на основе МДП-транзисторов. Процесс записи информации в триггер. Схема квазистатических триггеров. Применение триггеров в схемотехнике для построения сдвигающих регистров.

История компании LG

История компании LG началась с 5 января 1947 года, когда предприниматель Ку Ин Хой образовал компанию Lak Chemical Co.

Секретные машины

В 1960 году об этих машинах не писали. Строгой секретностью были окружены все исследования и разработки, непосредственно связанные с решением военных задач. Поэтому широкой аудитории сведения о специализированных машинах стали известны только в 90-е.

Принципы построения ОЗУ

Изучение принципов построения оперативных запоминающих устройств Цель работы: Изучение основных принципов построения оперативных запоминающих

Закон Мура

Основные характеристики компьютеров улучшаются в два раза каждые два года.

Логічні елементи

Дослідження базових елементів булевої логіки, для чого використовують логічні елементи потенціального типу на біполярних транзисторах (мікросхема К155ЛАЗ). Рівні відліків цифрового сигналу, відносно шасе. Допустима границя статичної завадостійкості.

История развития вычислительной техники 2 2

Text Text 1953-1955. IBM 604, IBM 608, IBM 702 1953-1955. IBM 604, IBM 608, IBM 702 1965-1966. БЭСМ-6 60 000 транзисторов 200 000 диодов 1 млн. операций в секунду память – магнитная лента, магнитный барабан работали дл 90-х гг. Graphics

Підсилювачі на НВЧ - транзисторах.

Лекція 31 . Підсилювачі НВЧ відрізняються від звичайних тим, що треба узгодити вхід-вихід та каскади. Наприклад розглянемо еквівалентну схему транзистора АП-326А: